Intel DCAI 2023 Update New Technology and Updated Xeon Roadmap

These days we have an update from Intel about its info center and AI organization. We had been pre-briefed on the update but will be masking the celebration are living. Expect to listen to a lot more about Intel Xeon roadmap updates as well as new technologies, like the MCR DIMM or Multiplexer Blended Ranks DIMM that we lined lately.

Be aware, this is remaining protected reside so you should justification typos.

Intel DCAI 2023 Update New Technologies and Updated Xeon Roadmap

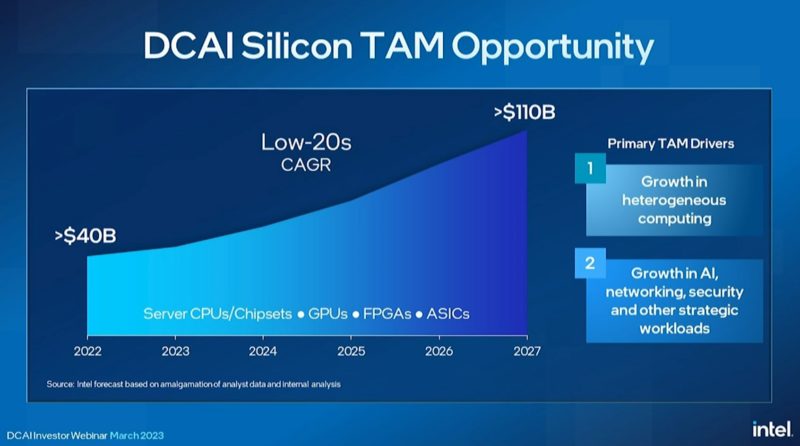

A major aspect of today’s party is focused on the trader group, so there is a significant part of this that is on the TAM for DCAI or current market possibility.

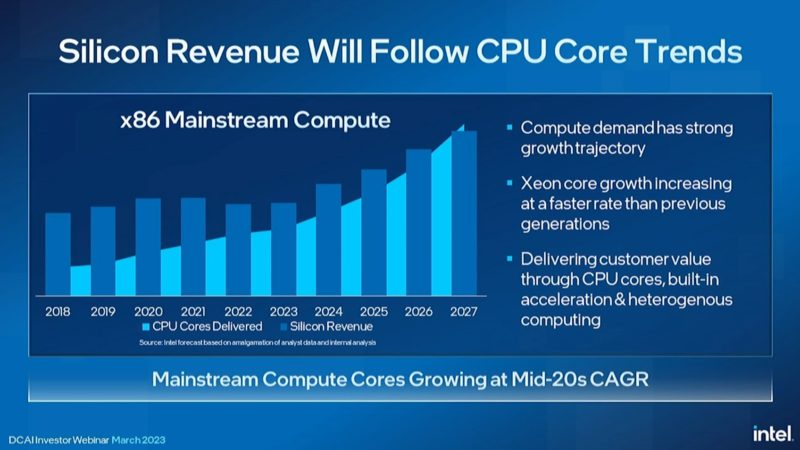

Intel said that it is going to maximize cores for every socket and so it expects its core advancement to follow sector developments even if sockets development is distinctive.

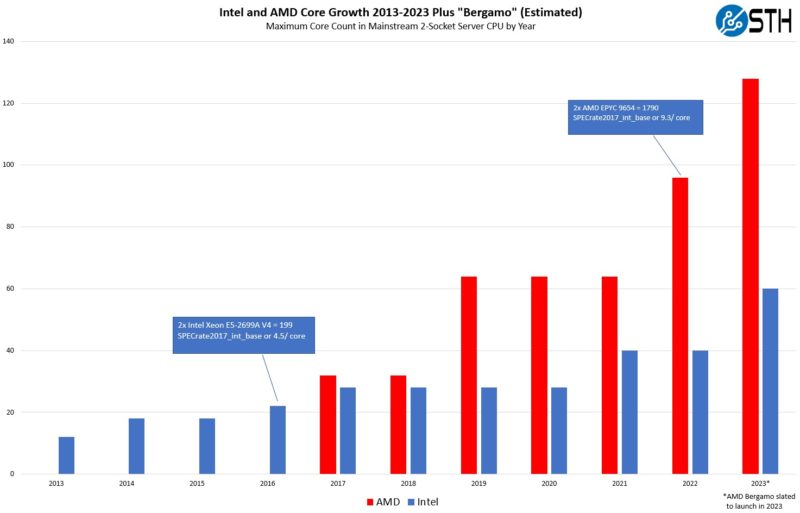

Intel states it is going to accelerate its core density more rapidly than it experienced been. Below is the Updated AMD EPYC and Intel Xeon Core Counts Over Time check out that we shared earlier this yr.

Intel stated it plans to raise ASP to seize the worth of having extra cores. It will also capture the price from other portfolio IP.

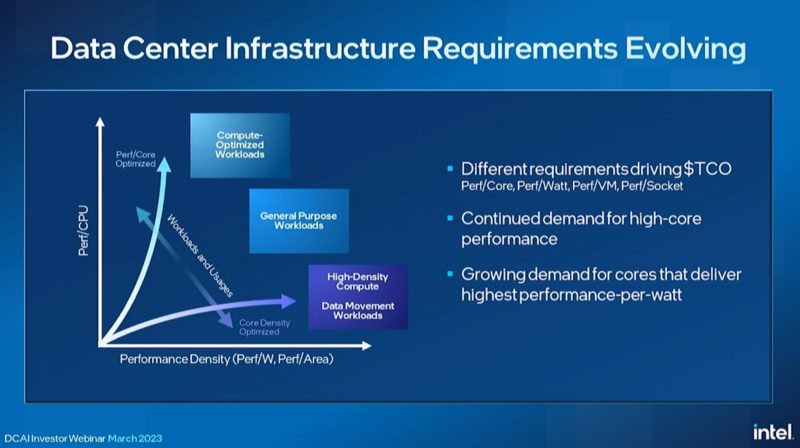

Intel states that the market has developed to support both of those bigger-functionality cores as very well as lessen-general performance dense cores.

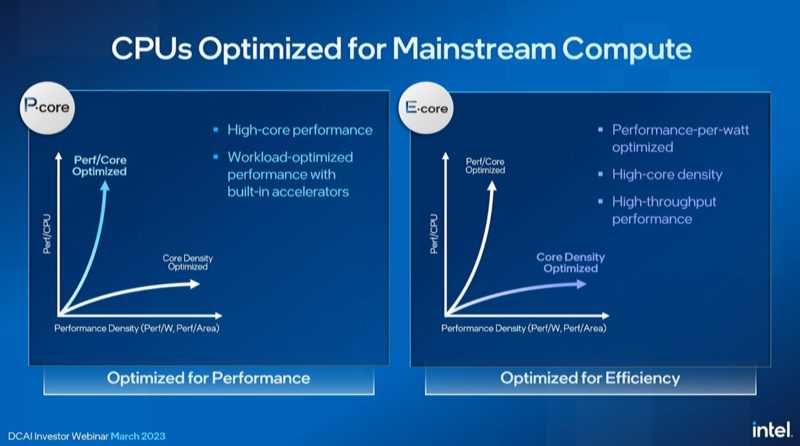

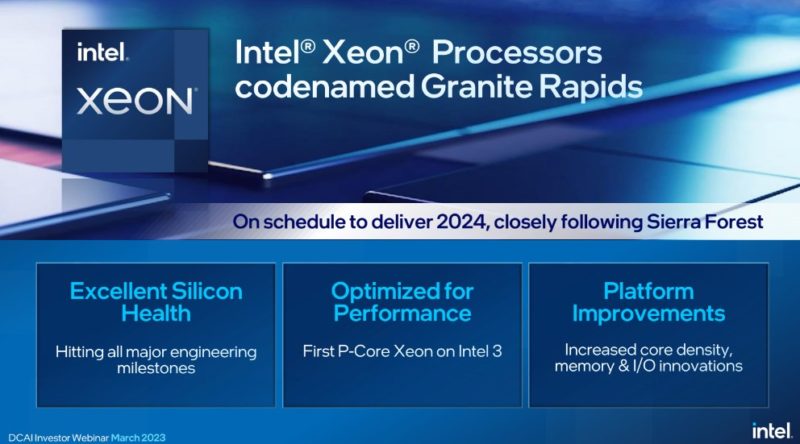

Intel is conversing about P-core “Rapids” products and E-core “Forest” chips.

Intel states it options to re-use I/O chiplets and memory controllers in between Rapids and Forest merchandise. Intel looks to be next AMD EPYC’s IO Die-like models.

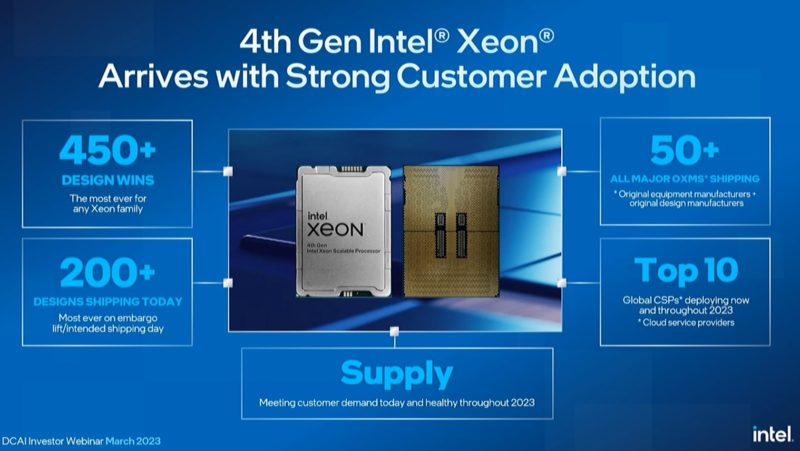

Intel suggests that it has 450+ 4th Gen Intel Xeon Scalable “Sapphire Rapids” designs, but a lot less than fifty percent of people are at this time in the marketplace. Intel suggests that the crossover for SPR volume will happen mid-yr. It also hopes when China comes back and when enterprises start out investing a lot less cautiously that it will assistance increase profits.

Intel is demonstrating a demo applying Intel AMX acceleration to demonstrate how its chips can be a lot quicker than AMD EPYC areas. You can learn far more about that in: Hands-on Benchmarking with Intel Sapphire Rapids Xeon Accelerators.

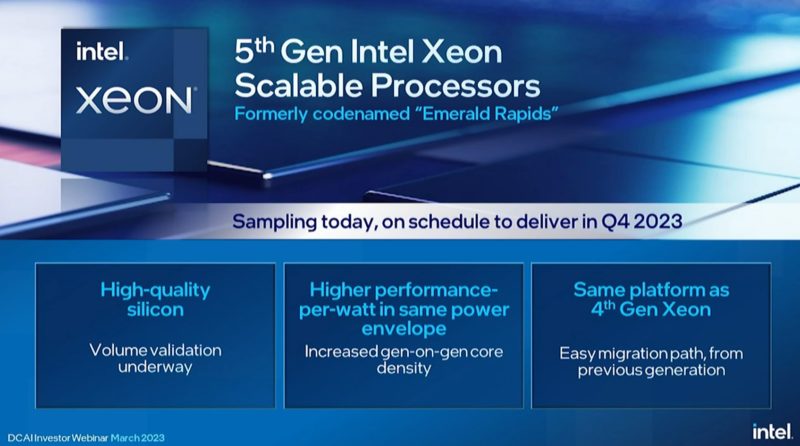

Later on this yr is the Emerald Rapids. Below is that chip. I missed the <5 second clip of the chip close up.

Emerald Rapdis will be the 5th Gen Intel Xeon Scalable series. It is a drop-in replacement for Sapphire Rapids servers. This is different than the Ice Lake generation which was a single-generation platform.

5th Gen Xeon Scalable will be on Intel 7.

Sierra Forest in the first half of 2024. Granite Rapids shortly thereafter. Granite Rapids will be on Intel 3.

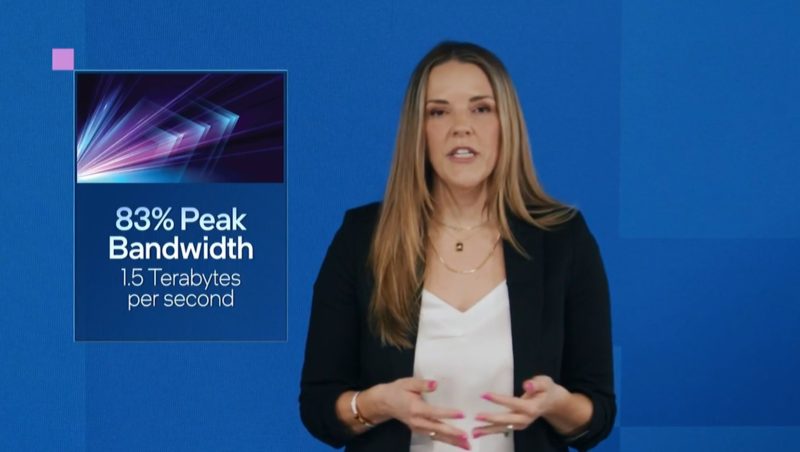

Granite Rapids will have MCR DIMMs. Those will offer 1.5TB/s of memory bandwidth in a dual-socket server.

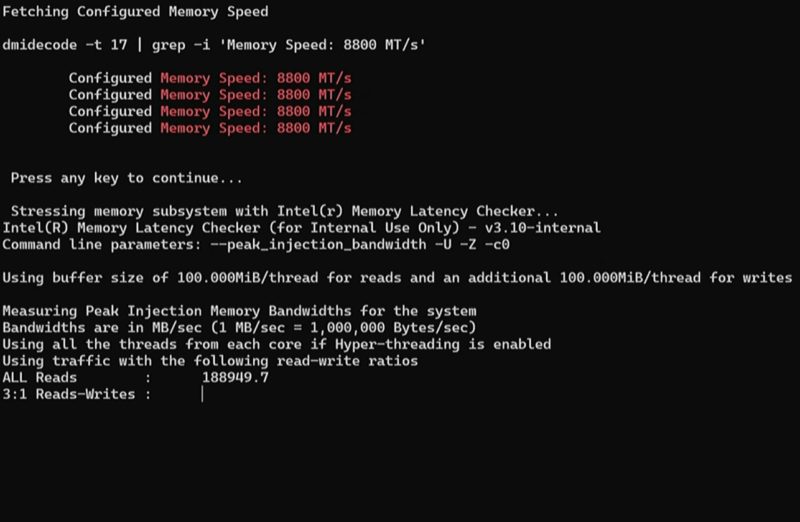

Here is DDR5-8800 running with Intel MLC:

Intel’s Sierra Forest is expected in 1H’24. We usually expect “1H” to mean June based on previous launches. This will be an Intel 3 platform.

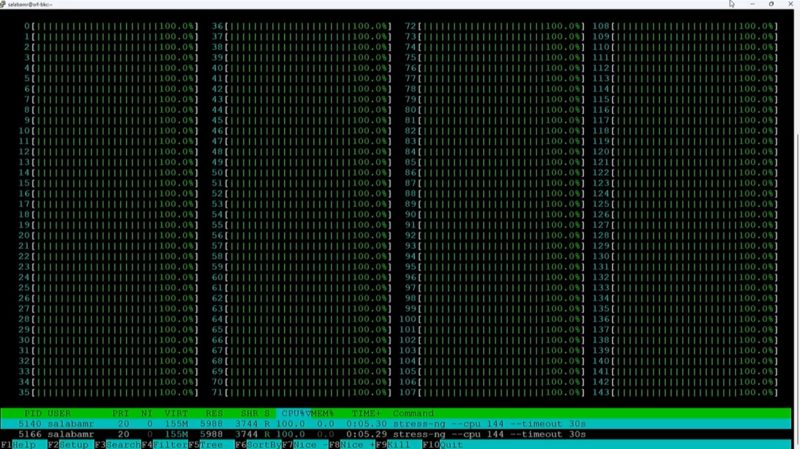

Sierra Forest is 144 cores and is booting OSes and running stress-ng.

Clearwater Forest in Intel 18A in 2025. This is the next E-core design.

Here is the Xeon roadmap between now and 2025.

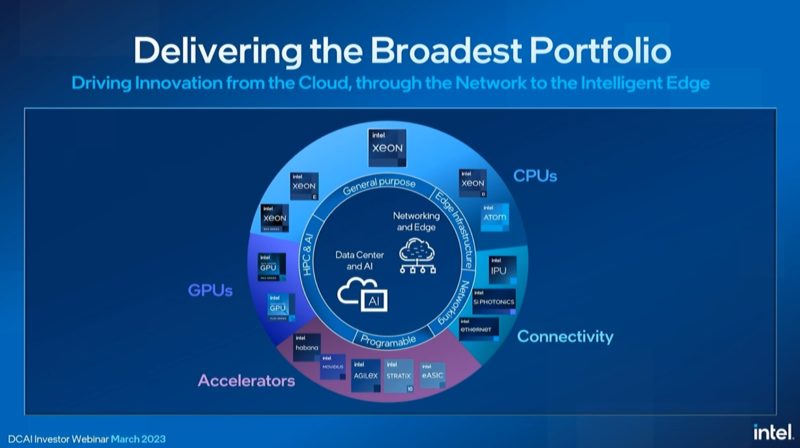

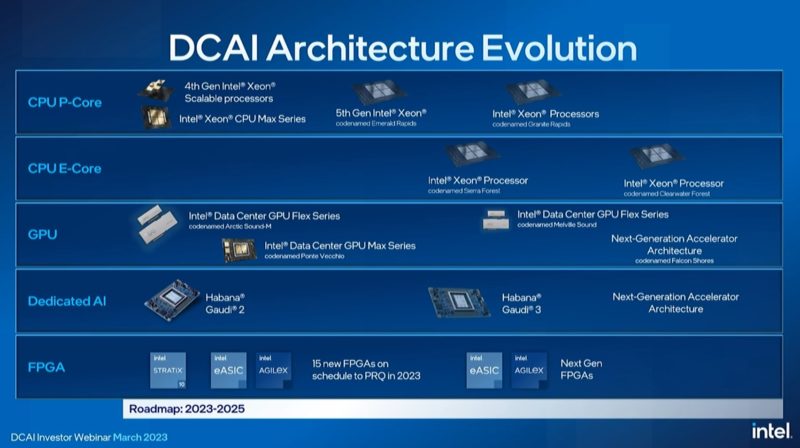

Here is the DCAI Roadmap including other products. I asked about the lack of HBM accelerators. Intel told me that they will be addressing higher performance memory updates in the future.

Something to note here is that the GPU, Habana Gaudi AI accelerator and FPGAs are continuing. 15 new FPGAs in 2023 is a lot.

Here is Intel’s AI Accelerator TAM:

Intel is talking about OneAPI and SYCL. The pace of this is fast enough that we are going to leave most of that for others since there is not as much being announced here and seems like it is more of a recap.

More to come as the event progresses.

Final Words

There is a lot in here. The P-core versus E-core mix is something we are really interested in at STH. Intel gave us a wide range of the expected future mix of P-cores versus E-cores that it could be shipping in a few years. To be frank, I am much more excited about Sierra Forest than Emerald Rapids at this point. As we increase the number of dedicated accelerators in the ecosystem, having E-cores alongside accelerators may make sense. Also, there are many servers simply running nginx serving web pages that do not need optimizations for high-performance computing.

I asked about what the IO Die or Tile will be called. Intel told me that the exact name is not finalized.